Learn. Verify.

Tape Out.

AI-assisted chip verification platform. Auto-generate test plans, testbenches, and coverage reports from your RTL. Open source, pluggable LLM, education-first.

module barrel_shifter_16bit (

input clk,

input rst_n,

input [15:0] data_in,

input [3:0] shift_amt,

input shift_dir, // 0=left, 1=right

output [15:0] data_out

);

reg [15:0] stage1, stage2, result;

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

result <= 16'b0;

else

result <= stage2;

end

assign data_out = result;

endmoduleAI-generated from: "16-bit barrel shifter with 2-stage pipeline"

One Pipeline. Full Verification.

From RTL input to coverage report, every step visualized and AI-assisted.

See It in Action

From RTL design to coverage analysis, every step in one platform.

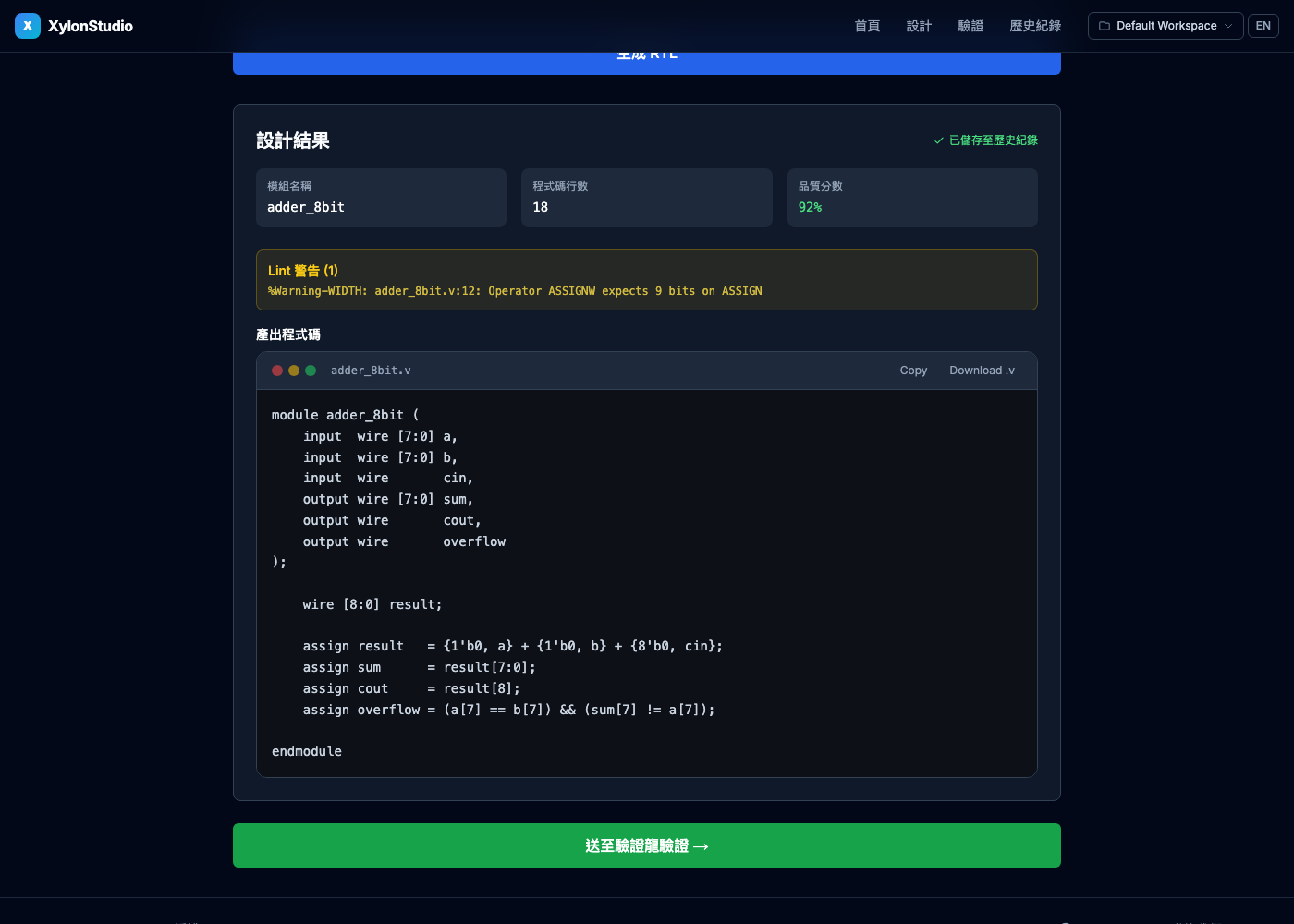

AI-generated RTL design result

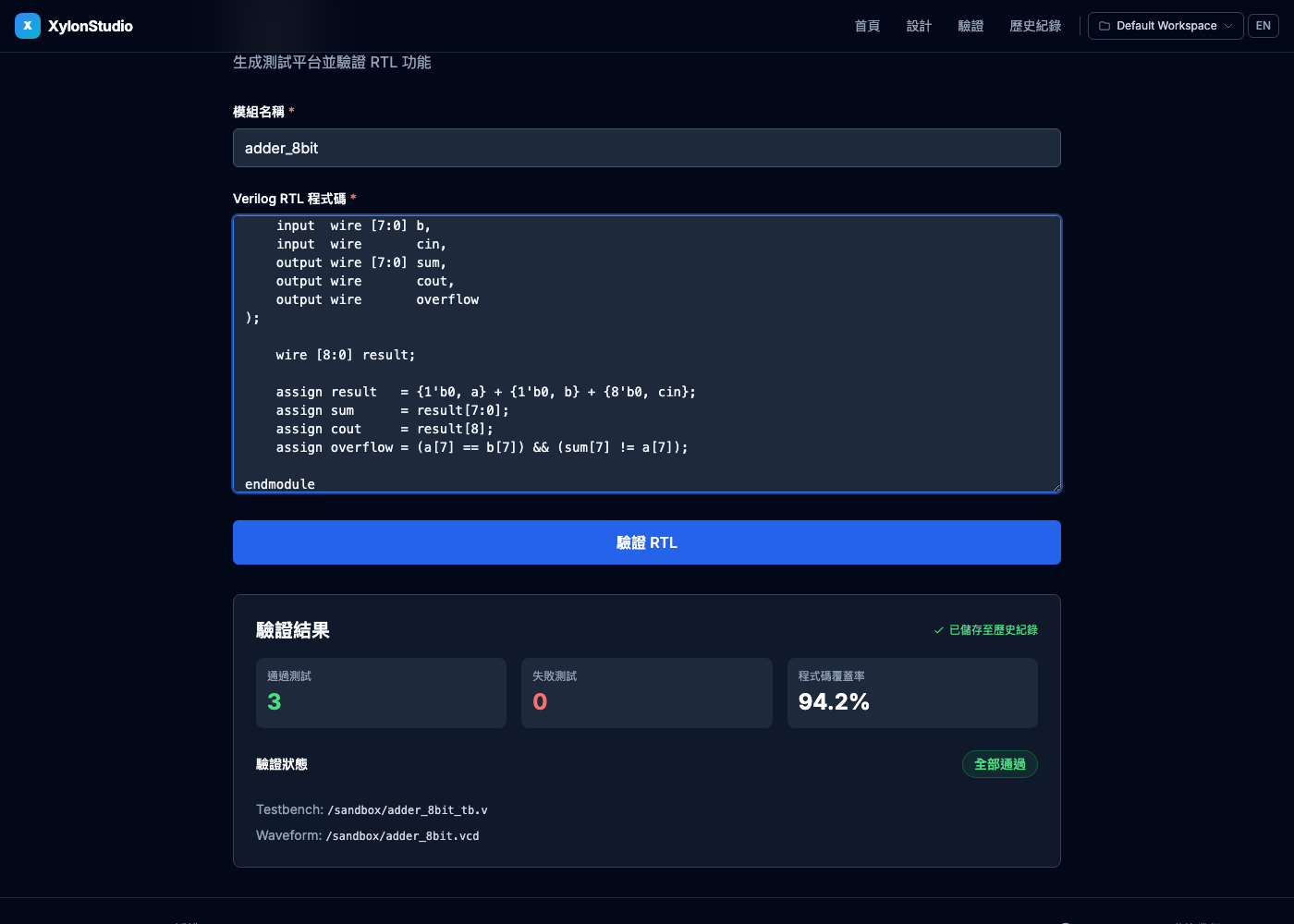

Automated verification with 94.2% coverage

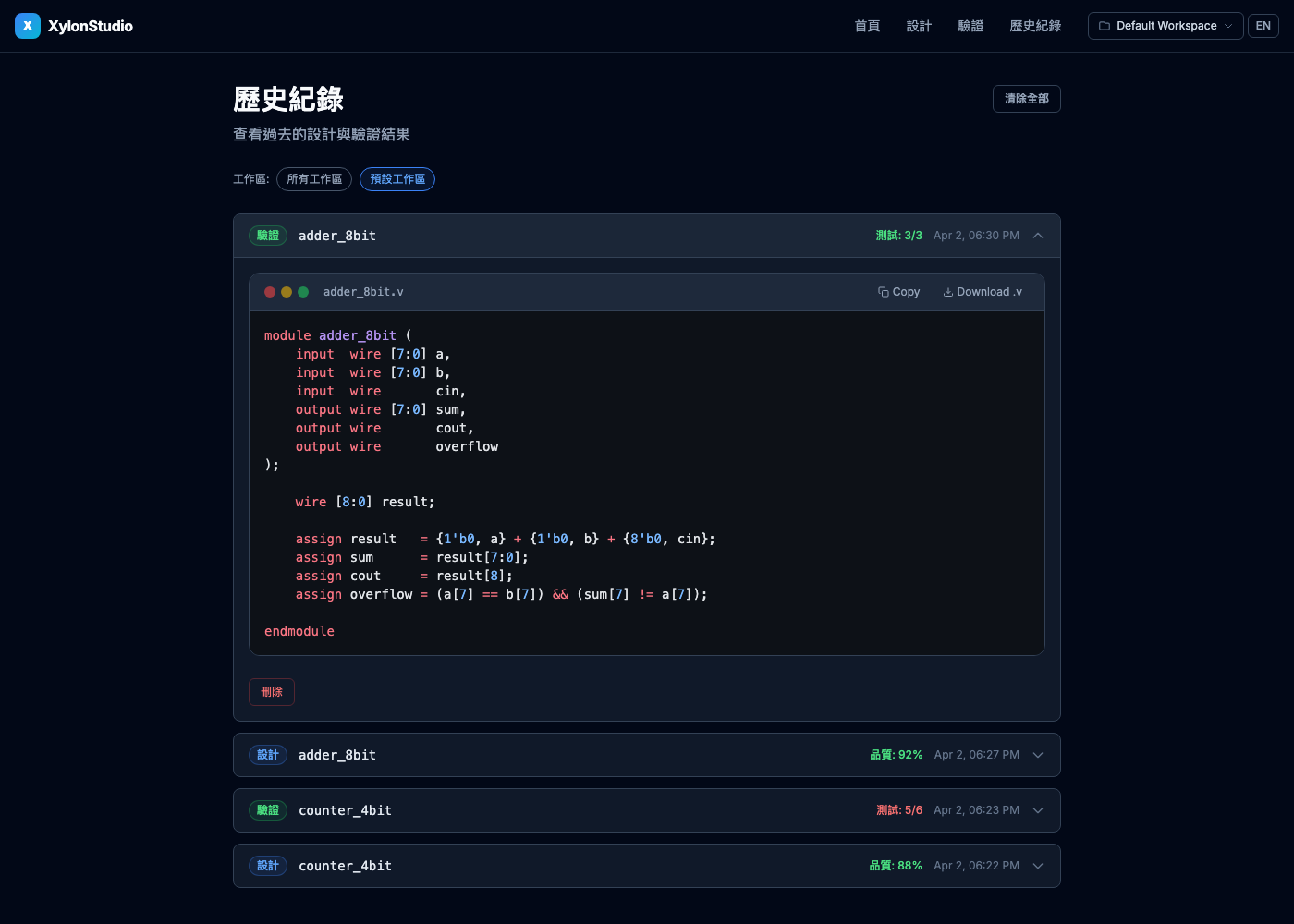

Design history and version tracking

Clean, modern interface

What XylonStudio Does

AI Test Plan Generation

Paste your RTL. AI analyzes ports, logic, and edge cases, then generates a structured verification plan. Learn what to test and why.

Testbench Auto-Generation

AI writes SystemVerilog testbenches from your test plan. Verilator compiles and simulates automatically. Coverage too low? It iterates.

Coverage-Driven Iteration

Real line, toggle, and branch coverage via Verilator. The pipeline loops until your coverage target is met or suggests what to test next.

Debug Assistant

Simulation failed? AI explains what went wrong in plain language, highlights suspicious signals, and suggests fixes.

RTL to Silicon

Synthesize with Yosys, place and route with OpenROAD. See your Verilog become a real chip layout targeting SkyWater 130nm.

Pluggable LLM

Use Claude, GPT, DeepSeek, Qwen, or Ollama. Self-host for IP protection. Your model, your data, your choice.

Built For

Students & Professors

Free, open source. Learn verification methodology with AI guidance. Pipeline visualization makes every step clear.

Junior DV Engineers

Accelerate testbench writing, understand coverage gaps, debug faster. On-premise deployment keeps your IP safe.

FPGA Developers

Open-source toolchain, no license fees. CLI and API for automation. Community-driven and extensible.

How We Compare

| Feature | XylonStudio | Commercial EDA | Manual Flow |

|---|---|---|---|

| Price | Free (MIT) | $100K-500K/yr | Free tools |

| Test Plan | AI-generated | Manual | Manual |

| Testbench | AI-generated + iterate | Manual UVM | Manual |

| Coverage | Verilator (auto) | Proprietary | Manual setup |

| AI / LLM | Pluggable (BYOLLM) | None / locked-in | None |

| Education Mode | Built-in | None | None |

Open Source. MIT License.

Core platform, pipeline engine, and all basic plugins are free and open source. Build on it, extend it, contribute back.

Get Early Access

XylonStudio v2 is under active development. Join the waitlist to be the first to try it.

No spam. Unsubscribe anytime.